# RABBLE 65

# **TECHNICAL MANUAL**

#### CONTENTS

## RABBLE 65

#### HARDWARE MANUAL

| CHAPTER | 1  | INTRODUCTION                 |

|---------|----|------------------------------|

| CHAPTER | 2  | PARTS LIST                   |

| CHAPTER | 3  | UNPACKING AND ASSEMBLY       |

| CHAPTER | 4  | POWER SUPPLY                 |

| CHAPTER | 5  | KEYBOARD                     |

| CHAPTER | 6  | VIDEO DISPLAY                |

| CHAPTER | 7  | RS232, CASSETTE INTERFACE    |

| CHAPTER | 8  | CENTRONICS PRINTER INTERFACE |

| CHAPTER | 9  | FLOPPY DISK CONTROLLER       |

| CHAPTER | 10 | 18 PIN INPUT - OUTPUT BUSS   |

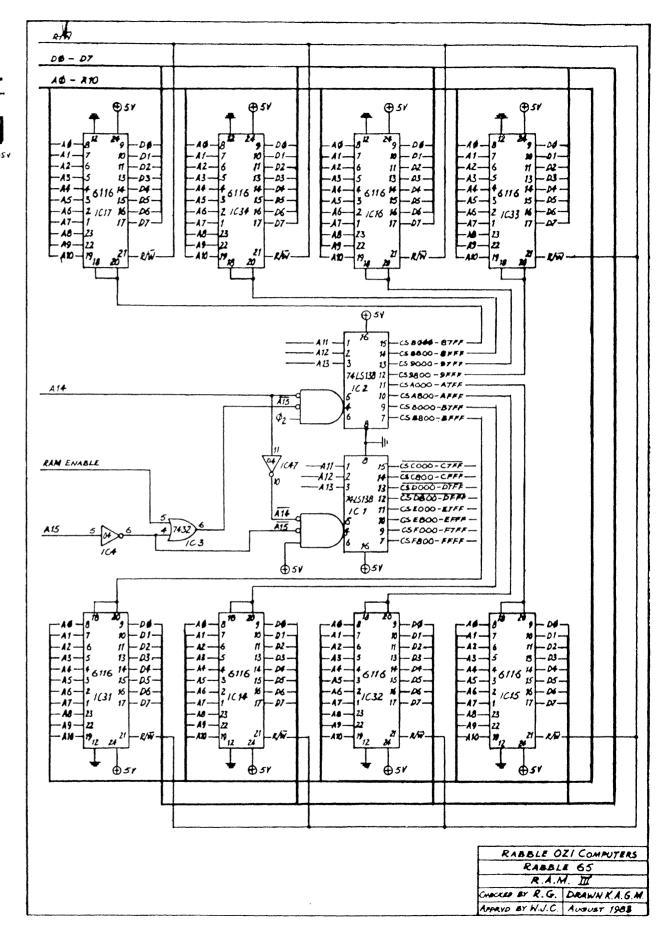

| CHAPTER | 11 | RAM                          |

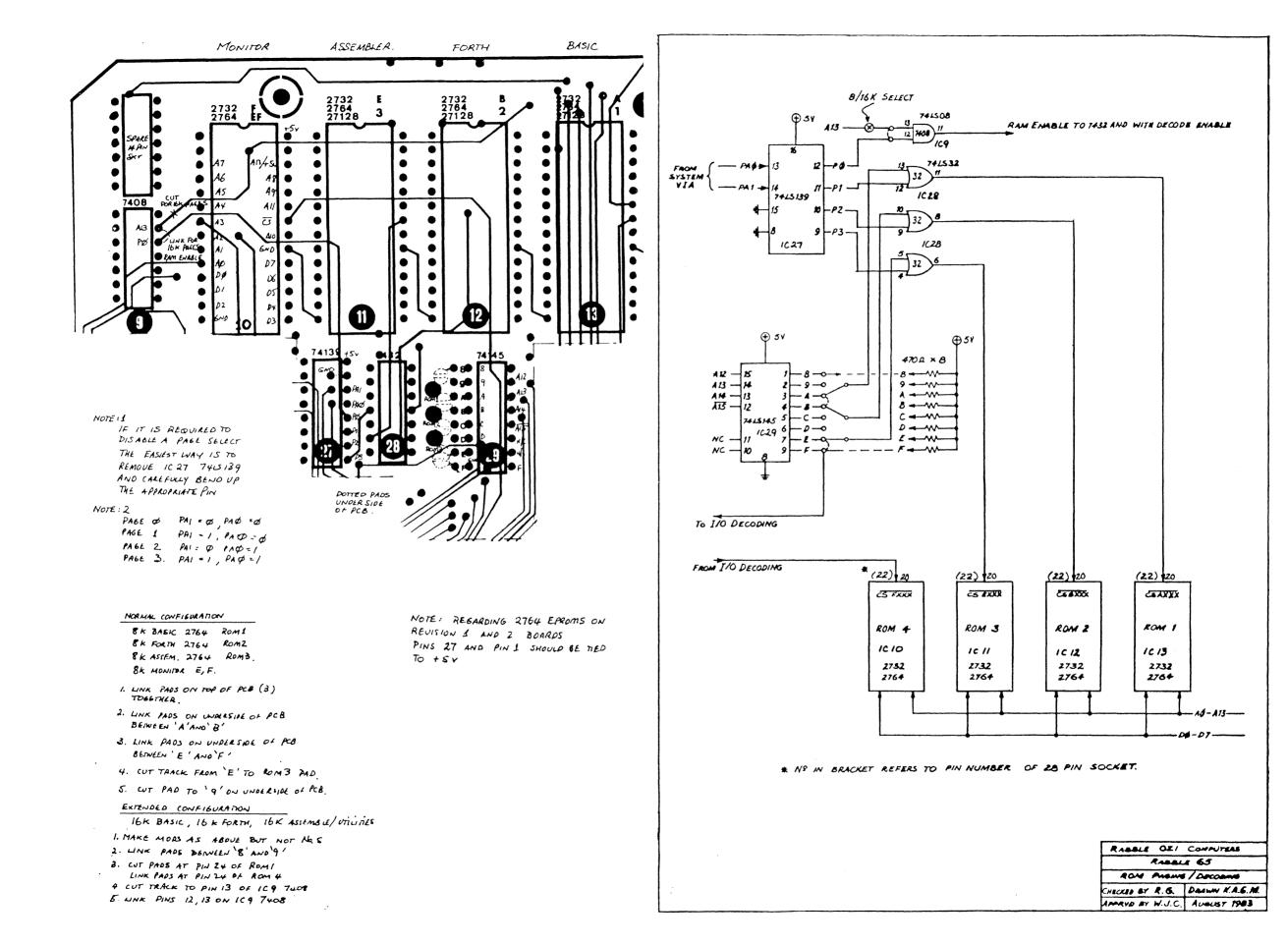

| CHAPTER | 12 | ROM                          |

| CHAPTER | 13 | CPU                          |

| CHAPTER | 14 | INPUT - OUTPUT DECODING      |

| CHAPTER | 15 | GLOSSARY OF TERMS            |

#### INTRODUCTION

The information contained in this manual outlines procedures to be followed in unpacking, assembling and operating your Rabble 65 microcomputer system. Please follow these instructions carefully. Preferably, you should pour yourself a long cup of coffee and read the manual completely before unpacking any of the components. This will ensure a better understanding of the system during assembly with a minimum of problems.

#### UNPACKING

Carefully remove the system components from their packages and save all packaging materials. They may be required later to return damaged or faulty components. Ensure that all components ordered are accounted for. Any deficiences or breakages should be referred immediately to your supplier.

#### DESCRIPTION

The Rabble 65 microcomputer, by Rabble Ozi Computers, has been designed and manufactured in Australia. It is a fully expandable system capable of rivalling any other system currently on the market. The Rabble 65 has been designed as a single board system with a seperate and easily relocatable keyboard. The overall size of the main printed circuit board is 370 mm x 320 mm

A full size keyboard is provided to ensure compatability with most operating systems. The full upper and lower case character set is available. The Rabble 65 keyboard is a software scanned or polled keyboard, which offers greater flexibility to the user in designing application software.

The video display is generated by a Cathode Ray Tube Controller chip, the MC 6845. This is configured to provide a display format of 25 rows of 80 characters. The CRTC is supported by a character generator providing 256 characters, which include all ASCII characters as well as numerous games, symbols and elements. These provide sufficient variety to be able to construct chess board pieces or even space ships and tanks.

The video output is a composite video signal suitable for coupling directly to a video monitor via an RCA connector. A monitor is recommended to ensure the resolution that the Rabble 65 is capable of providing. Lesser quality will be experienced with modified TV sets.

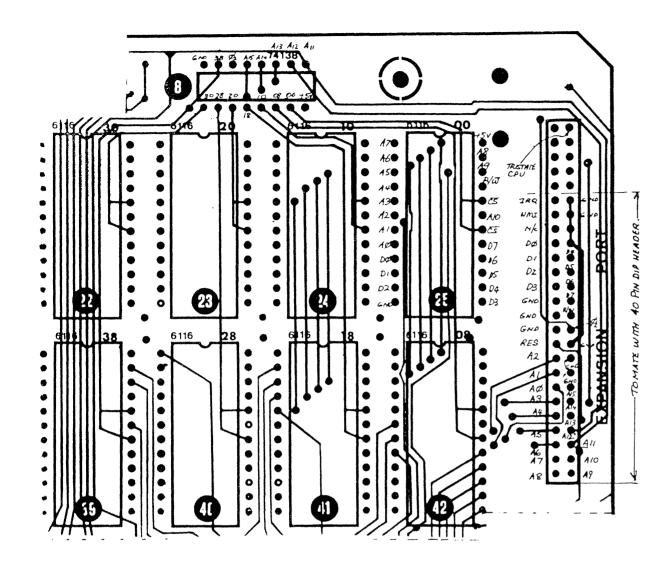

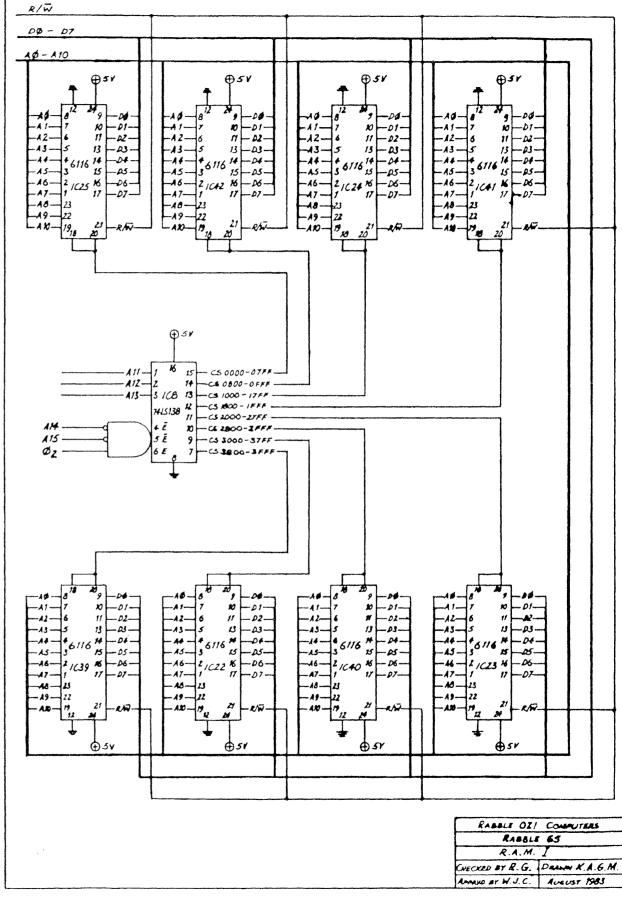

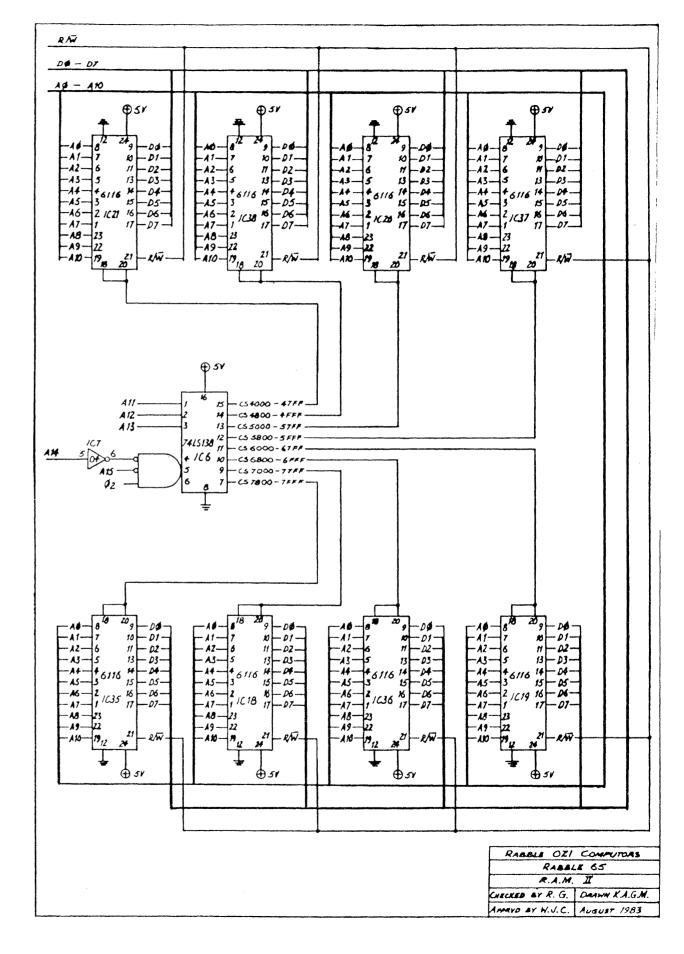

The Rabble 65 will support, contiguously, up to 48K of CMOS RAM and a further 4K of CMOS RAM is provided for on the board. 2K of the latter RAM is for the video display and the other 2K for user/system RAM which is cold start protected from BASIC. You can place your special user routines here without overwriting them with BASIC. The CMOS RAM is located at the following locations:-

| 0 - 49151     | 0000 - BFFF | 48K Contiguous RAM in 2K blocks |

|---------------|-------------|---------------------------------|

| 51200 - 53247 | C800 - CFFF | 2K system/user RAM              |

| 53248 - 55295 | D000 - D7FF | 2K video RAM                    |

| 57344 - 61439 | E000 - EFFF | Optional user ROM               |

| 61440 - 65535 | F000 - FFFF | System Monitor ROM ( RA-65 )    |

HEX

A total of 56K of ROM is provided for on the Rabble 65. The RA-65 monitor is provided with all systems and provides the user all the facilities required to operate and write machine code programmes, as well as to provide the disk system boot functions. This system monitor is detailed explicitly in the System Software Manual. The 56K ROM is acheived by paging the memory block from \$8000 - BFFF in three pages, and selecting an 8K block from \$E000 - FFFF. A fourth block of 16K is made available for RAM. The paging is discussed in more detail in chapter 12.

A host of peripheral devices are supported by the Rabble 65. The first of these is the Floppy Disk Controller, which can operate up to four disk drives. These drives can be 5 1/4" or 8", single sided or double sided with AC or DC driven motors. An on board data separator is provided for as well as a motor control for DC driven drive motors. The Rabble 65 is Ohio Scientific compatible and will boot up their popular software packages 65DV3.2, 65DV3.3, and many others with minimal modification. Refer to the System Software Manual for details on these.

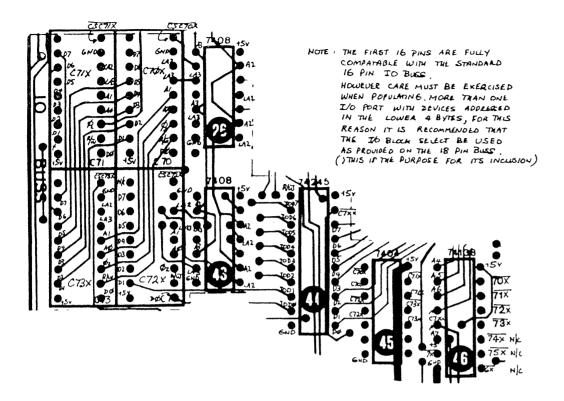

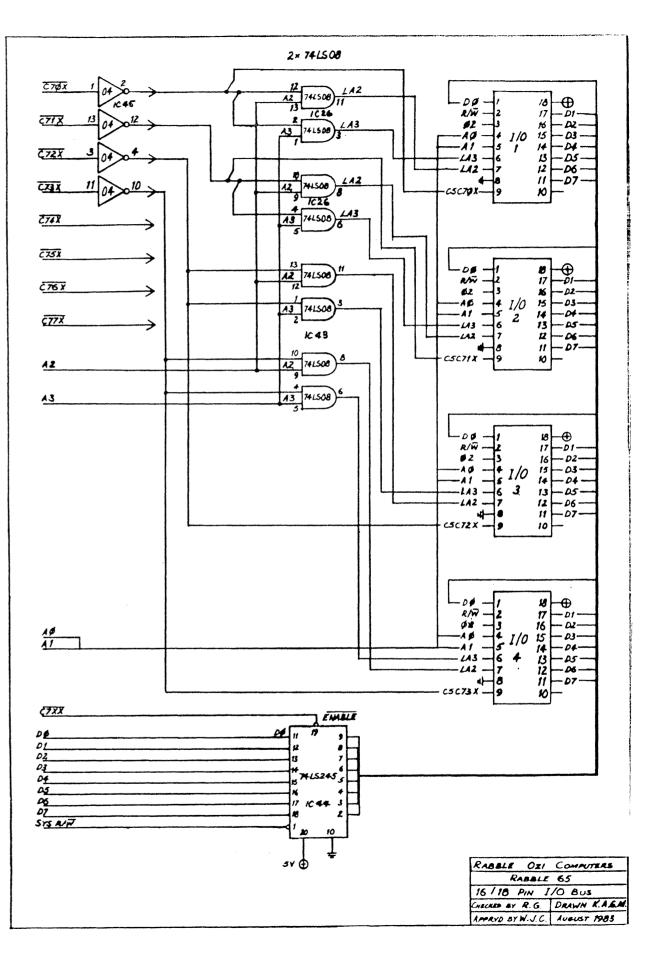

Other I/O support includes an on board RS232 port with a selectable baud rate generator and a casette port which will operate with a standard low cost domestic casette recorder. Two expansion busses are provided for. A 16/18 pin I/O Buss provides a fully decoded port system to drive up to eight ACIA's (serial I/O ports) or a number of other directly accessable I/O devices. These devices are not provided on board but are available separately. 16/18 pin expansion devices available, or soon to be released, include a High Resolution colour graphics board, an EPROM programmer, programmable sound generators, voice recognition, Votrax SCO1 speech generator, prototype breadboard, and many others. The second buss system is a 50 way buss which provides full access to the microcomputers control and data buss, permitting expansion to occupy the total available memory, or for multiprocessor operation.

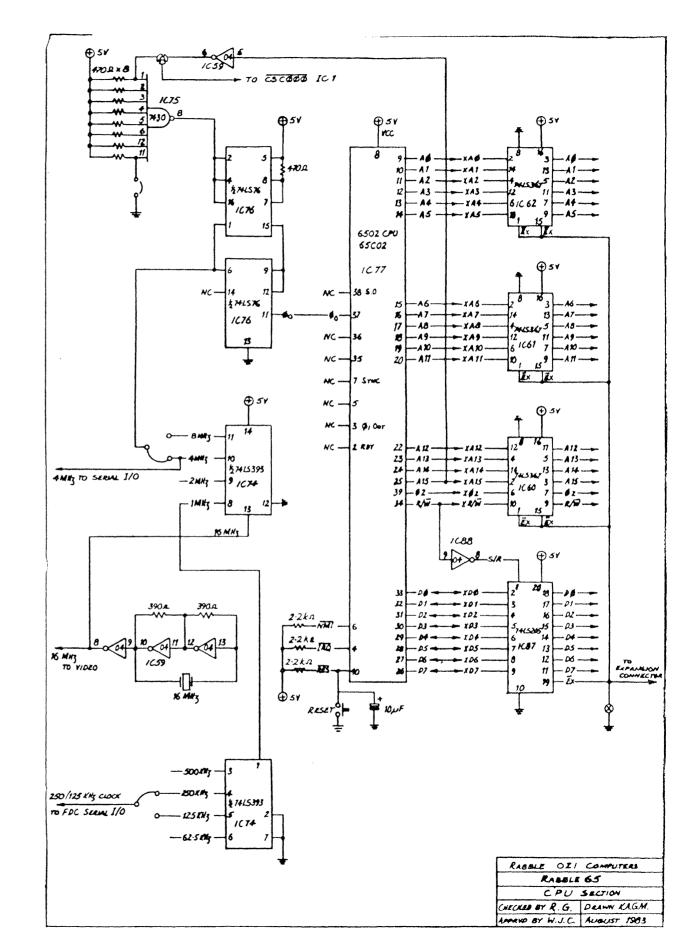

The heart of this Rabble 65 is controlled by a CPU chip manufactured by a number of sources and numbered "6502", later versions will employ an updated version of this chip manufactured by Rockwell, the "65C02".

This manual does not give programming details to the user on any of the languages mentioned. Anyone wishing to become proficient in programming in any of the high level languages or in machine code are advised to purchase a book on that language which is available from many bookshops and written by numerous people. However, many of the words

. . . .

02....

DECIMAL

03.... contained in the manual, which may be new to you, are explained in the Glossary elsewhere in this manual.

. . . .

MEMORY MAP

| $\mathbf{F}$ | F | F | F |

|--------------|---|---|---|

|--------------|---|---|---|

|              | System Monitor RA65                                                                                                                                                                                 | 8K ROM                                                                                     |                                           |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------|--|--|

| E000<br>DFFF |                                                                                                                                                                                                     |                                                                                            |                                           |  |  |

| D800<br>D7FF | Not allocated.                                                                                                                                                                                      |                                                                                            |                                           |  |  |

| D000<br>CFFF | Video Display Memory                                                                                                                                                                                |                                                                                            |                                           |  |  |

| C800<br>C7FF | 2K CMOS RAM                                                                                                                                                                                         |                                                                                            |                                           |  |  |

|              | System Input Output                                                                                                                                                                                 |                                                                                            |                                           |  |  |

|              | C73x 18 pin buss n<br>C72x 18 pin buss n<br>C71x 18 pin buss n<br>C70x 18 pin buss n<br>C4xx 6532 RIOT key<br>C0 6x 6522 VIA key<br>C01C-F 6845 CRTC v<br>C010-3 6850 FDC AC<br>C000-3 6821 FDC PIA | umber 3<br>umber 2<br>umber 1<br>poard control<br>pard and auxillary sy<br>ideo controller | ystem control                             |  |  |

| C000<br>BFFF | System one<br>Top of <b>4</b> 8K RAM                                                                                                                                                                | System two<br>Top of 8K ROM<br>3 pages                                                     | System three<br>Top of 16K ROM<br>3 pages |  |  |

| A000<br>9fff |                                                                                                                                                                                                     | Start 8K ROM pages<br>Top of 40K RAM                                                       |                                           |  |  |

| 8000<br>7FFF | Top of 32K RAM                                                                                                                                                                                      |                                                                                            | Start 16K ROM pages                       |  |  |

| 3FFF         | Top of 16K RAM                                                                                                                                                                                      |                                                                                            |                                           |  |  |

| Olff         | Stack                                                                                                                                                                                               |                                                                                            |                                           |  |  |

| 0100<br>00FF |                                                                                                                                                                                                     |                                                                                            |                                           |  |  |

| 0000         | Page Zero                                                                                                                                                                                           |                                                                                            |                                           |  |  |

#### CHAPTER 2

#### PARTS LIST

Integrated Circuits

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                                      | Qty.                                                     | Socket No.                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Type<br>74LS00<br>74LS02<br>74LS04<br>7406<br>74LS08<br>7416<br>7417<br>74LS20<br>74LS27<br>74LS20<br>74LS27<br>74LS32<br>74LS138<br>74LS138<br>74LS138<br>74LS138<br>74LS138<br>74LS139<br>74LS145<br>74LS157<br>74LS163<br>74LS163<br>74LS175<br>74LS175<br>74LS245<br>74LS374<br>74LS374<br>74LS374<br>74LS393<br>NE556<br>DM8602<br>CD4040<br>CD4051<br>CA3130<br>MC1488<br>MC1489<br>2764<br>2764<br>6116LP3<br>6502<br>6522<br>6532 | Qty.<br>928131551112241483313112233112211111111111111111 | Socket No.<br>49,53,65,83,99,105,106,1<br>84,92.<br>4,7,45,47,51,59,88.<br>117.<br>9,26,43.<br>81.<br>78,79,89,91,101.<br>48.<br>52.<br>75.<br>3,28.<br>82,103,104,110.<br>76.<br>63,95,98,100.<br>1,2,6,8,46,50,66,67.<br>27,68,90.<br>29.<br>54,55,56.<br>58.<br>69.<br>85,86.<br>44,73,87.<br>60,61,62.<br>71.<br>74,112.<br>116.<br>102.<br>96.<br>97.<br>64.<br>93.<br>94.<br>10.<br>70.<br>11,12,13.<br>14-25,30-42,72.<br>77.<br>107.<br>108. | <pre>ll,113. System Monitor. Character System Languages. CMOS RAM. CPU. VI A. RIOT.</pre> |

| 6821<br>68 <b>4</b> 5                                                                                                                                                                                                                                                                                                                                                                                                                     | 2<br>1                                                   | 80,109.<br>57.                                                                                                                                                                                                                                                                                                                                                                                                                                       | PIA.<br>CRTC.                                                                             |

. . . .

| 06  |   |   |   |   |

|-----|---|---|---|---|

| ••• | • | • | • | • |

ACIA.

. . . .

IC Sockets

Connectors

50 way 36 way 20 way

| 8 1 | PIN | 1  |

|-----|-----|----|

| 14  | PIN | 44 |

| 16  | PIN | 30 |

| 18  | PIN | 4  |

| 20  | PIN | 4  |

| 24  | PIN | 29 |

| 28  | PIN | 4  |

| 40  | PIN | 6  |

Resistors 5% 0.25W

| 47<br>100<br>150<br>390<br>1K<br>2.2K<br>3.3K<br>5.6K<br>10K<br>15K<br>10K<br>470K<br>470 x 9 | 3<br>1<br>2<br>9<br>4<br>3<br>2<br>2<br>1<br>1<br>2<br>3<br>7 | Bourns 4310R-101 Resistor SIP                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 470 x 9<br>10k                                                                                | 5                                                             | Cermet trimpot VTP Linear                                                                                                                                                                      |

| Capacitors<br>68pf<br>100pf<br>150pf<br>220pf<br>1nf<br>100nf<br>1uf<br>10uf                  | 1<br>1<br>2<br>1<br>6<br>20<br>1<br>20                        | 630V ceramic subminiature<br>630V ceramic subminiature<br>630V ceramic subminiature<br>630V ceramic subminiature<br>100V polyester film<br>100V polyester film<br>35V Tantalum<br>25V Tantalum |

| Miscellaneou                                                                                  | S                                                             |                                                                                                                                                                                                |

| IN914<br>Pushbutton<br>Crystal                                                                | 3<br>1<br>1                                                   | Diodes<br>SPST PC mounting<br>16MHz                                                                                                                                                            |

5WRowNED 2 shielded DIP headers 1 shielded DIP headers 2 shielded DIP headers

07.... DB25PSAA 1 RS232 08.... CHAPTER 3

#### GENERAL ASSEMBLY INSTRUCTIONS

This board has a very high density of packages and trackwork. For this reason it is not recommended for beginners to cut their teeth on. Warranty claims for damage caused by poor user workmanship will not be honoured. Experienced kit builders will require the following tools to assemble the Rabble 65 successfully:-

Temperature controlled soldering iron with a tip diameter of 2.4mm or less

A cloth or wiping sponge to keep the tip clean

A desoldering tool or solder wick

1.25mm or 0.71mm 60/40 resin core solder

Small pair of diagonal cutters and long nose pliers

Test equipment should consist of a multimeter, oscillascope, frequency counter and logic probe.

Before starting assembly, check the board carefully for any shorted, open circuit or damaged tracks. All care is taken in the production of these boards. Any faults can be repaired before construction or returned for replacement.

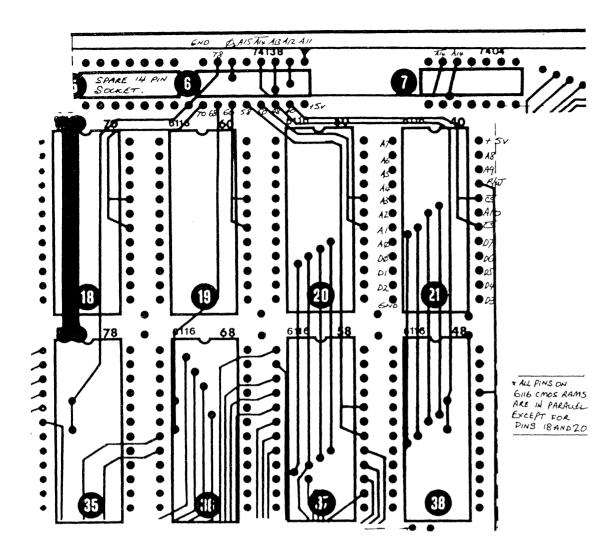

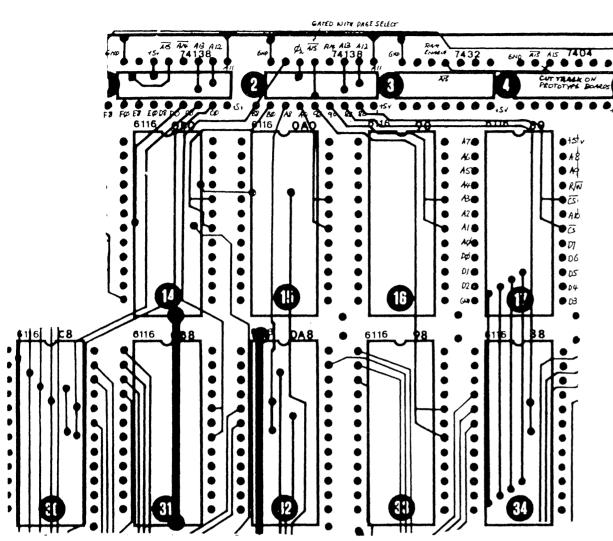

Fit and solder IC sockets to the board first. We recommend the use of sockets wherever possible, as servicing at a later date becomes a much simpler task. Solder each pin of each IC socket only on the underside of the board, as the holes are plated through the board, making connection with the other side. Do not miss pins because of an apparent pad with no tracks radiating, a track will most likely be attached on the top side of the board. Follow this with the fitting of all resistors, capacitors, resistor packages and other discrete components, including peripheral sockets.

It is recommended that all discrete components and sockets be fitted at this stage to provide for each upgrading of the Rabble 65 at a later time, by simply plugging in chips.

. . . .

After all components have been soldered into position, inspect each solder joint carefully to ensure no dry joints exist. Check also for solder slivers which may cause problems and remove, solder blobs covering more than one pin of an IC are also a hazard to beware of.

Any resin deposits on the board can be cleaned off at this stage by wiping the affected spots with a cotton bud dipped in methylated spirits.

When satisfied that all the above is of a high standard, you can mount the keyboard. This is not an easy task as there are over 100 pins to be fitted into over 100 holes at once, without missing any. First ensure that all pins on the base of the keyboard are erect, after removing the foam packing from the bottom. If any are not erect, carefully bend them until they are. It is best to lay the keyboard on a soft but firm surface with the key tops down and the space bar facing you. Turn the keyboard PCB over and carefully align the holes over the keyboard pins and fit the keyboard. Force should not be used in this operation. When the board is fully seated over the keyboard, solder two terminals, one at each end of the keyboard, to hold things in place and check that all pins of the keyboard have been fed through the board. If not, untack the keyboard, clean the plated through holes, repair the keyboard and try again. When fitted correctly, solder all connections on the keyboard then check and clean if necessary.

To facilitate the ease of construction, the rest of the assembly instructions will be described in logical sub-assemblies, where a circuit description will be given at the same location. We believe that this will provide an easier to follow method of assembly as well as giving a better understanding of how the computer operates.

The description will be broken up into 16 parts to describe the eleven major sections of the computers main board. These major sections are:-

1 Chapter 4 Power Supply Keyboard, and system VIA, and RIOT - - - 22 Chapter 5 parts Video display controller - - - 2 parts 3 Chapter 6 4 Chapter 7 Serial I/O 5 Chapter 8 Centronics port Chapter 9 Floppy disk controller - - - 2 parts 6 16/18 pin I/O bus 7 Chapter 10 RAM - - - - 3 parts 8 Chapter 11 9 Chapter 12 ROM 10 Chapter 13 CPU

. . . .

09....

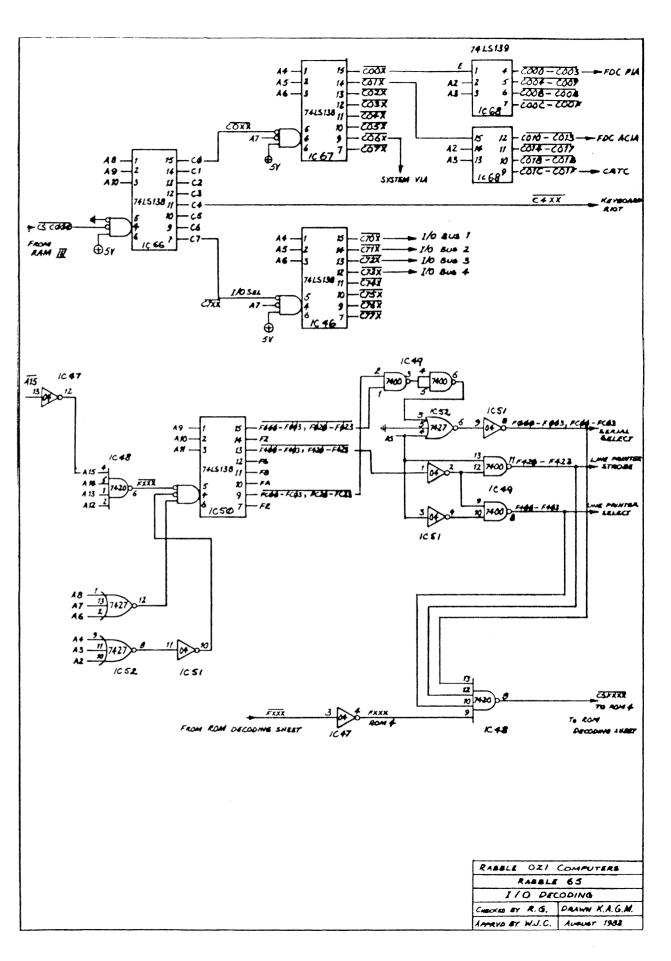

#### 11 Chapter 14 I/O Decoding

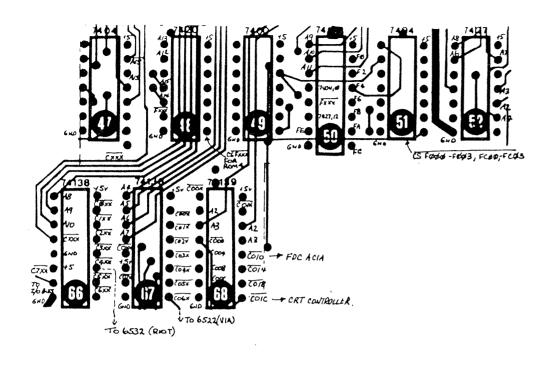

Each major section of the computer description shows in detail the relevent section of the circuit and component layout. A full circuit description, together with setup and alignment instructions are included, as well as fault location details.

11.... CHAPTER 4

POWER SUPPLY

The Rabble 65 power supply is a high voltage switch mode supply. It is provided as a sealed unit, which should be returned to your supplier for service if required. This style of power supply has been chosen for its high efficiency and reliability.

The efficiency of this type of power supply comes from the use of a high frequency switching oscillator, driving a ferrite core power transformer. The resultant low voltages are then rectified and because of the high frequency ripple, only a small amount of filtering is required.

| Input voltage   | 240 VAC                        |

|-----------------|--------------------------------|

| Output voltages | +5.0<br>+12.0<br>-12.0<br>-5.0 |

The power supply is capable of operating the fully populated CPU board as well as two 5.25" floppy disk drives.

#### CIRCUIT DESCRIPTION

The AC voltage is fed via a mains filter into a bridge rectifier to provide a DC supply which is then capacitively filtered. This DC voltage drives an oscillator at a frequency of around 20KHz, this varies with actual load. The oscillator output is then fed to the ferrite core transformer, with it's many windings. The secondary outputs are then rectified in the normal manner to provide unregulated supply outputs which are filtered with electrolytic capacitors. The +5 volt output is fed to a voltage sensing network, which constantly monitors the output voltage, and when it rises above +5 volts it turns on a LED within an opto coupler. The transistor in the opto coupler then causes the oscillator to shut down and thus the secondary voltage starts to decrease. When the +5 volt supply starts to drop below +5 volts the LED turns off and the oscillator starts up again. As the +5 volt supply is controlled by the primary winding of the transformer, all secondary windings will be regulated simultaneously.

#### CAUTION

The Rabble 65 power supply contains high voltages within the case. Many of the components are at mains potential, and specialised equipment 12.... is required for servicing. There are no user adjustments inside. Should your power supply develop a fault, DO NOT OPEN OR ATTEMPT TO REPAIR. Send your power supply to your Rabble 65 dealer for service.

For 8" floppy disk drives, it is neccessary to provide an additional power supply to drive the solenoides and drive motor.

For a single 8" slimline drive in the standard Rabble 65 CPU case, a 24 volt supply at 1 Amp will be required. This supply is of conventional design, and fits into the CPU case with the floppy disk drive.

If twin 8" drives are being implemented, then a separate case is required to house these drives, for both slimline or standard size drives. The power supply for these drives will be fully self contained within the drive enclosure. It is of conventional design and delivers +5volts at 2 Amps and +24 volts at 2 Amps. CHAPTER 5

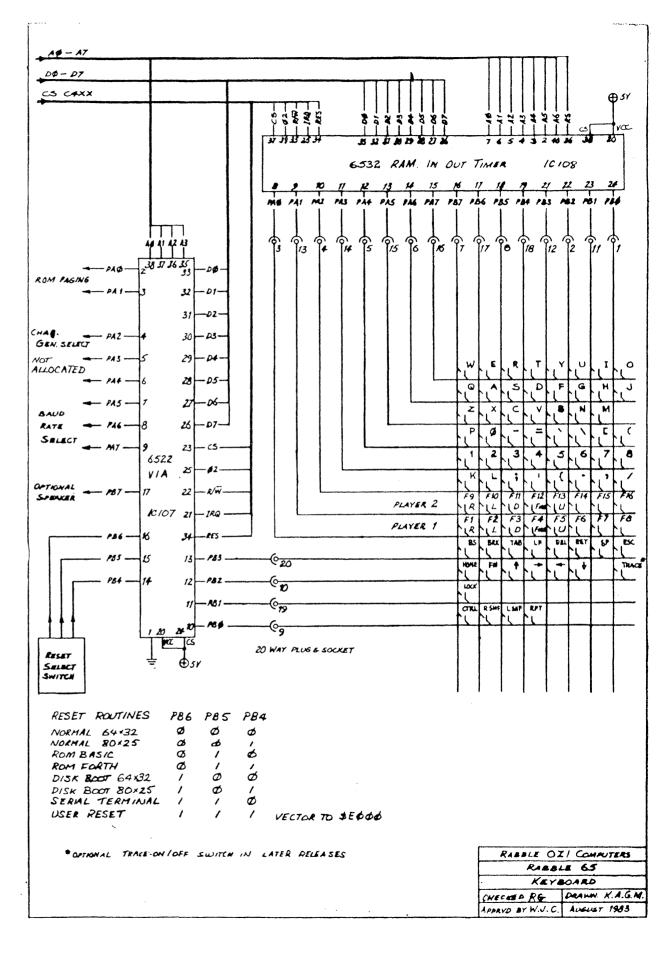

#### KEYBOARD CONTROLLER

#### ASSEMBLY

The keyboard should already be mounted as detailed in the general assembly instructions. Fit 40 pin sockets for IC's 107 and 108, fit a 20 way DIP header to the CPU board just below IC 108. The other 20 way DIP header should be fitted to the keyboard assembly. Insert a 6522 into socket 107 and a 6532 into socket 108 to complete assembly.

#### CIRCUIT DESCRIPTION

The keyboard is encoded in a  $12 \times 8$  matrix, of which not all combinations are used, to provide a comprehensive ASCII character set. The keyboard has its eight columns read by the system RIOT, IC 108, on port B and port A reads the first eight rows of characters needed by the keyboard. A further four rows of characters and control functions are input to the system VIA IC 107, port B bits 0 - 3.

The VIA, 6522 - IC 107, is located at \$C060 (Port B I/O register) and the RIOT, 6532 - IC 108, registers at \$C480 for port A and port B at \$C482.

When any key is pressed, it connects one of the column lines at the RIOT, port B, to one of the row lines of the RIOT, port A or the VIA port B.

The monitor reads the keyboard by accessing each column in turn, then reading the row port to ascertain if a key has been pressed on that row, if not it checks the next row and so on. Once the key has been found, the monitor returns the ASCII value for use by the computer programme.

The 6532, RIOT, also contains 128 bytes of RAM located at \$C400 - \$C47F, decimal 50176 to 50303. This area of RAM is used by the system monitor for system control and operation and is not generally available for user software use.

#### DEBUGGING

The keyboard should be checked if only one character is not being received. The method of doing this is to turn the power off and remove IC's 107 and 108. Then locate the offending key on the keyboard circuit and find which port inputs refer to it, and measure the resistance whilst holding the key depressed. For example, key "1" is located at intersecting points of RIOT PB7 and PA3, corresponding to pins 16 and 11 of IC 108. Measure at this point and a closed circuit should appear with the switch pressed and an open circuit with the key released. For the space bar, the column is PB1, IC 108 pin 23 and the row is VIA, PB3, IC 107 pin 13. If it appears that the key is faulty, repeat the resistance check at the rear of the P.C.B. directly behind the suspect key. If this checks OK, then there is a faulty track. If the fault is still evident, remove the key cap carefully and check the alignment of the contacts, if necessary clean the contact by inserting a piece of thin card ( a corner of a business card is ideal ), between the contacts and gently wipe them without applying any side pressure.

If more than one key is defective, note down all the defective keys, and it will most probably be that they will all be related to one port line, refer to the keyboard circuit. Check the common line from the keyboard to the appropriate pin of the VIA or RIOT and repair if necessary. If this does not cure the defect, then it is probable that the VIA or RIOT is faulty and should be replaced, only if it appears that one port line is affected.

If the keyboard does not appear to function at all then check that the control lines to the VIA and RIOT are present.

|                  | RIOT       | VIA   |

|------------------|------------|-------|

| Phase two clock  | pin 39     | 25    |

| Register select  | <b>3</b> 6 |       |

| Read/wr ite      | <b>3</b> 5 | 22    |

| Data lines D0-D7 | pins 33-26 | 33-26 |

| Address lines    | 7-2, 40    | 38-35 |

| Chip select      | " 37       | 23    |

Follow up any missing signals, and if all present, replace the RIOT first, then if necessary, the VIA.

#### THE KEYBOARD

The Rabble 65 has a built in 62 key typewriter-style keyboard. The keyboard is read by polling the rows and columns that the keys are

. . . .

14.... connected to. This method of reading the keyboard is extremly economical as the 62 keys can be individually read with only 20 wires arranged to connect the keys in a  $12 \times 8$  matrix.

The matrix is connected to the ports of a 6532, RIOT, and 6522, VIA, where the software / monitor reads which column and which row have been connected together. Once a key has been read into the RIOT and VIA, the monitor converts this value to ASCII value for use by the computer. The RIOT for the keyboard is located at \$C4XX which is decimal 50176, The VIA for the keyboard is located at CO6X which is decimal 49608

Some of the keys on the keyboard do not generate on ASCII code, but instead are used to extend the range of control of the keyboard.

CONTROL and SHIFT are used to modify the codes produced by the other keys. The chart, below, shows the codes produced when SHIFT or CONTROL are pressed with another key.

The RIOT contains 128 bytes of RAM as well as the input output ports as found on the 6521 and 6522, a timer is also included within this chip although it is not utilised in our application.

The RAM is used as a line buffer for keyboard entry, and this is located from C400 - C47F

Sixteen function keys are provided for. These keys are along the top of the standard keyboard, and labelled Fl through to Fl6. They provide the ability to customise software for ease of operation, whilst permitting great flexibility in the control of the system.

The function keys have been extended to provide external control of the keys Fl - F5 and F9 - Fl3. The connectors for these keys are suitable for joystick controls, making games software much more realistic in operation. CHAPTER 6

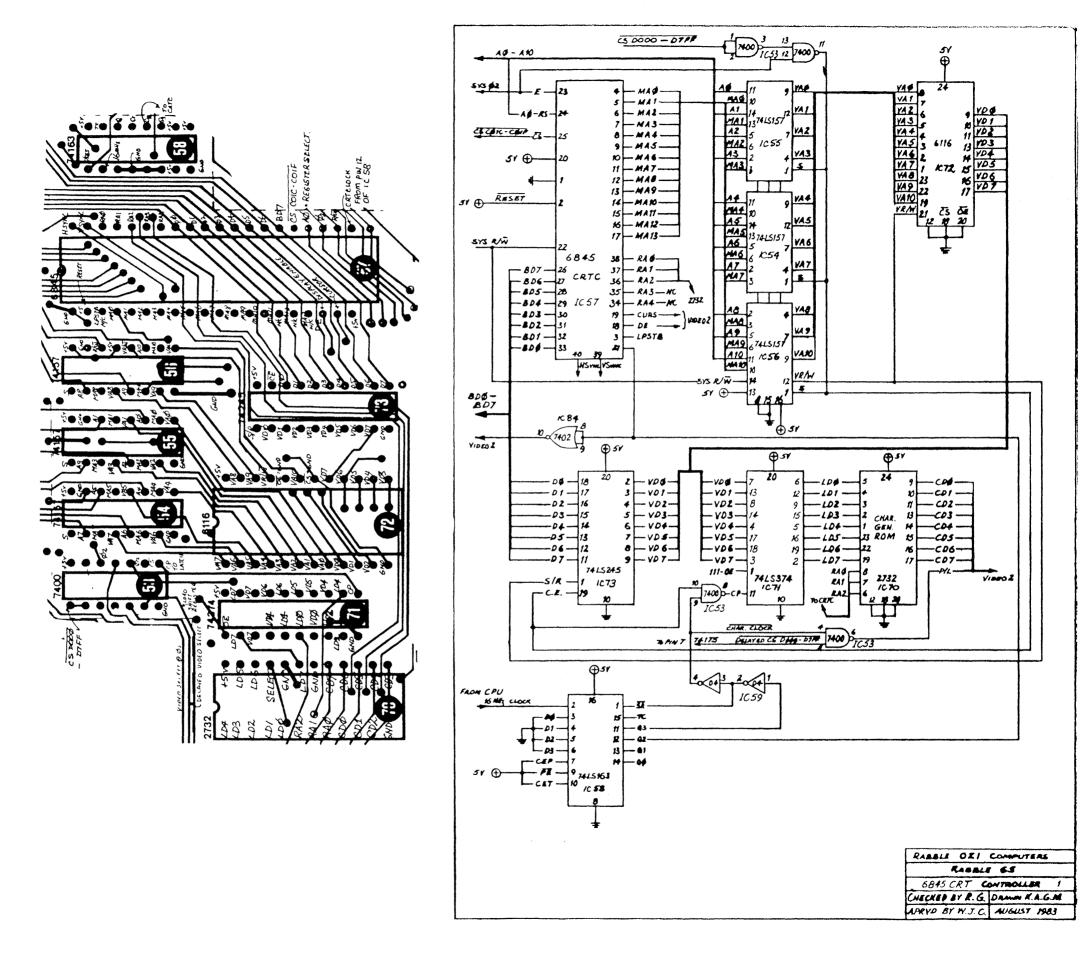

VIDEO DISPLAY CONTROLLER

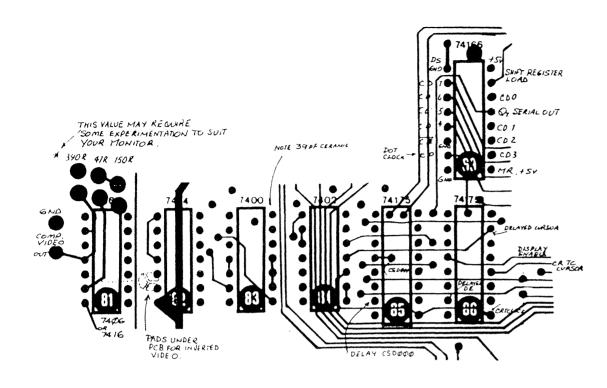

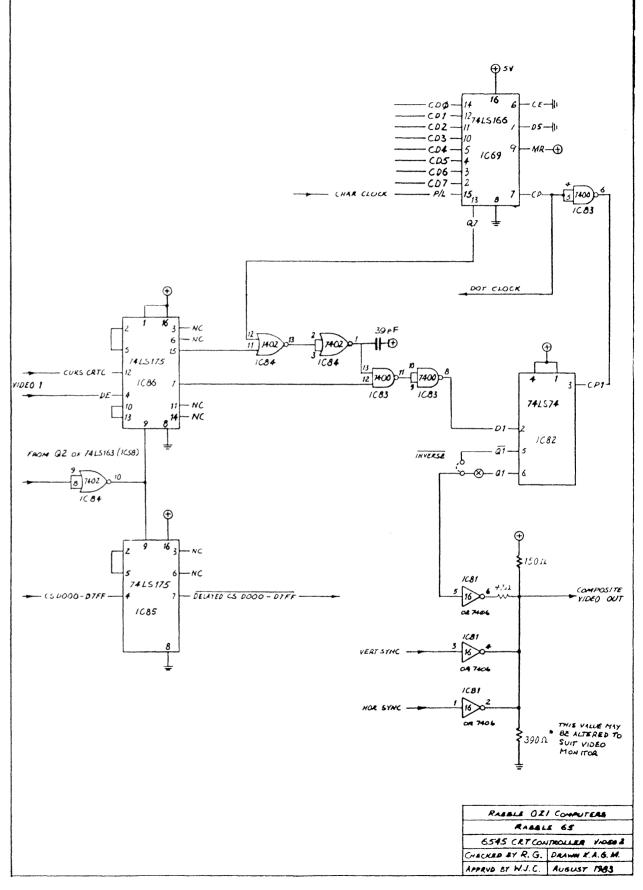

#### ASSEMBLY

The video display controller is the most complex section of the Rabble 65. There are 17 chips used in this section of the computer, and to facilitate the assembly and gain an understanding of the operation, the circuits have been split into two areas. These are the parallel and serial sections.

The parallel side of the video display controller deals with the data from the CPU buss and the CRTC in the parallel mode, prior to conversion to serial format. This includes the converting of ASCII data to the video character data. The serial section contains the parallel to serial shift register delay lines, buffering, and vertical and horizontal sync. mixing.

. . . .

To assemble, the following sockets must be fitted:-

| Parallel stage |      | 53 - 58 Inclusive<br>70 - 73 Inclusive |

|----------------|------|----------------------------------------|

| Serial stage   | IC's | 69 and 81 - 86 inclusive               |

Note the orientation of all sockets. To avoid later confusion, pin No. 1 of each socket is located towards the back edge of the board. The IC type No. is printed at the pin one end of the chip. Install the 3 resistors and the video connector.

After all components are soldered in place, inspect that no solder splashes, blobs etc. exist. Clean down any resin deposits by carefully wiping with a cloth dampened with methylated spirits.

Insert each chip into its appropriate socket to complete assembly. There are no hardware adjustments to be made to the video display controller as the CRTC is a software controlled device.

VIDEO DISPLAY

| DISPLAY TYPE     | : | MEMORY MAPPED SYSTEM RAM \$D000 - \$D7FF                     |

|------------------|---|--------------------------------------------------------------|

| DISPLAY CAPACITY | : | 2048 Characters                                              |

| CHARACTER SET    | : | UPPER and LOWER CASE ASCII and GRAPHICS                      |

| CHARACTER TYPE   | : | 8 x 8 DOT MATRIX                                             |

| VIDEO OUTPUT     | : | lv P-P COMPOSITE VIDEO                                       |

| DISPLAY FORMAT   | : | 64 CHARACTERS x 32 ROWS<br>80 CHARACTERS x 25 ROWS (Software |

| selectable)      |   | SO CHARACIERS & 25 KOWS (SOILWAIE                            |

Connection of the Rabble 65 to the video display monitor is via an RCA phono jack on the rear of the computer case. Your connector cable will be required to mate with the RCA phono jack to be compatible with your monitor at the other end.

It is recommended, for best results, to use a high quality video monitor rather than a converted TV set for your video display. The dot rate of our video generator is running at 16 Mhz, whereas few TV sets are designed to run at more than 4 Mhz. This does not mean that a TV set will not operate, however, the definition of the data on screen will be poor. For the same reason we do not recommend the use of VHF/UHF modulators

ъ,

SCREEN FORMAT

15...

The screen format is set up for 32 rows of 64 characters per row. This is the standard format for all standard application programmes. Another format is provided for in the system ROM, it is 80 x 25 for those wishing to operate their Rabble 65 as a terminal. To select the 80 x 25 screen format, the system monitor reads the system VIA Port B, bits 4 -6. The system is initialised according to the code on these lines. For further information on the initialisation options, refer to the chapter on the keyboard.

#### SCREEN MEMORY

The video display requires 2048 bytes of RAM, IC 72, located at \$D000 - \$D7FF. The video display uses this RAM to store information required to be printed on the screen. The CRTC, IC 57, cathode ray tube controller, takes the information from the memory and sends it to the character generator which converts the ASCII data to a format suitable for conversion to serial format to provide the dot information on the screen. A dot is sometimes referred to as a pixel or picture element.

The character generator provided with the Rabble 65 is a 2732 ROM. This ROM has 512 individual characters stored for use by the user. The ASCII character set in upper case, lower case and many control and function signs are implemented, together with numerous graphics symbols to provide adequate animation facilities for the user. The video character generator is used to store two sets of characters, of which only one set is available at a time. The selection of the alternate character set is controlled by bit 2 at port A on the system VIA located at \$C06X. A high on this bit selects the alternate character set. The standard character set, which is initialised on reset is selected with a low bit on Port A, bit 2 of the VIA.

#### CIRCUIT DESCRIPTION

The CRTC based video is capable of receiving a digital input, processing it, and displaying the appropriate alpha numeric or graphic data on a video monitor. The timing for the system is derived from a dot clock oscillator. The frequency of the dot clock is 16 Mhz, and this is used to drive the whole Rabble 65. The dot clock is fed to the 74LS166, IC69, parallel to serial shift register to control the rate of flow of information to the screen. The dot clock oscillator is divided down to generate the character clock. Thus for an 8 x 12 dot character display format the dot clock is divided by 8 to produce the character rate clock. The divider used for this purpose is a 74LS163, IC58, synchronous 4 bit counter. The 4 Mhz output of the counter is fed to the 6845, IC57, and is used for the CRTC clock where all the timing within the video system is referred. Each character rate clock increments the address lines (MAO -MA10) of the 6845. The 6845 has 13 address lines, our application uses 10 of these.

The video display RAM must be able to be accessed by both the CRTC

and CPU. Therefore, the address lines are multiplexed between the two devices via the 74LS157's,IC's 54, 55 and 56. The CPU takes control of the memory only during periods of reading from or writing to the video memory. The output of the multiplexer drives the RAM address lines.

The 2K x 8 static display memory is a CMOS 6116LP3 RAM chip as used throughout the Rabble 65. This memory requires lines which select a particular memory location within the RAM. The output of the display RAM (the data buss) is fed to an 8 bit latch (74LS374), IC 71, and is clocked into the latch on the next character clock. The character clock is used to latch the data into the 74LS374, IC 71. This creates a delay of one character clock from the time an address becomes valid to the memory, until the data is presented to the character generator ROM. The character clock also loads the parallel data from the character clock delay. Once the shift register. This produces a second character clock is used to shift data from the shift register to the video driver in serial format.

The display enable, DE and cursor, CURS, output signals are synchronous with the CRTC address lines. These signals are delayed by two character clock pulses to produce the signals on the video screen at the correct spots. To produce the required delay the signals DE and CURS, are fed via two flip flops (74LS175) IC 86, each clocked by the character clock, and the outputs are then fed into the video driver. The video signal is the combination of the shifted data ORed, IC 84, with the cursor and then ANDed, IC 83, with the display enable. This is fed into a 74LS74, IC 82, "D" flip flop and the signal is clocked out by the dot clock, to the open collector inverter, IC 81, this signal is then mixed with the H sync, and V sync, to provide a composite video signal suitable to drive a video monitor.

The CRTC generates character row addresses (RAO - RA4) for the character generator ROM. Selection of these addresses is synchronised within the CRTC by the horizontal sync pulse (H sync). The row address is incremented by one each H sync.

When the CPU is required to read from or write to the display RAM. the address multiplexer is switched to the CPU address lines. Since the display memory is located from \$D000 to \$D7FF, the chip select line (CS) labelled D000 is used to connect the address buss and the data buss to the CPU's busses. The address buss is connected to the video RAM via three 74LS157's, IC's 54, 55 and 56, two to one demultiplexers, the data buss is connected via a tri-state bidirectional buffer 74LS245, IC 73. With the data and address buss connected to the CPU, the video RAM is under the control of the CPU and the contents of the video RAM is treated as ordinary read-write memory. However, it is usual to store only information for display on the VDU in this RAM.

The 6845 CRTC, IC 57, used on the Rabble 65 is a software controlled device and can thus be programmed for screen formats other than the 64 x 32 and 80 x 25 which we have provided. Further formats and function changes can be invoked by the user. The CRTC has an address register that can point to any one of eighteen buried registers within the CRTC. Some of the variations which can be invoked by altering the registers which are addressed within the block COIC - COIF, decimal 49180 - 49183, are

17....

a screen format of 256 characters per row and 128 rows per screen. The horizontal and vertical sync positions are programmable, this allows the movement of the standard screen format to centre it on your monitor if necessary. Size and format of the displayed character block can be altered to provide a myriad of formats. The cursor can even be programmed to blink.

The registers in the CRTC are labelled R0 - R17, the following list briefly describes the function of each, and the value it contains for the Rabble 65  $32 \times 64$  screen format.

RO - HORIZONTAL TOTAL REGISTER which contains the sweep plus retrace time of one horizontal line

R1 - HORIZONTAL DISPLAY REGISTER - contains the number of characters to be displayed per row and should not exceed 80% of the value in RO.

R2 - HORIZONTAL SYNC POSITION REGISTER is programmed in character times and should be positioned such that it will occur slightly after the CRT beam is driven past the right edge of the screen.

R3 - HORIZONTAL SYNC WIDTH REGISTER also in character times, should be longer than sync circuitry in your monitor. It is normal for the value in RO to be greater than the sum of R2 and R3.

R4 - VERTICAL TOTAL REGISTER contains the number of character rows per screen, which is equal to the number of scan lines divided by the height of the character block.

R5 - VERTICAL ADJUST REGISTER holds the number of scan lines not required for display purposes.

R6 - VERTICAL DISPLAYED REGISTER has stored in it the number of character rows that are required for display.

R7 - VERTICAL SYNC POSITION REGISTER is programmed in

19.... character times and sets the position of the vertical sync pulse. The value must be equal to or greater than that of R6, but not too much greater than R6, lest the bottom rows will disappear.

> R8 - INTERFACE MODE REGISTER set the screen for normal sync, interlace sync or interlace sync and video. Normal sync writes to the screen with repetitive vertical sweeps which are not interlaced. Interlaced sync produces a similar display to the previous method but with interlaced raster scans. The last method, interlaced sync and video produces half height characters.

R9 - MAX SCAN LINE REGISTER holds the total number of scan lines per field.

R10 - CURSOR START REGISTER set the scan line on which the cursor will begin. One bit of this register specifies wether the cursor will blink or not, and another bit sets the blink rate at 320 ms or 640 ms.

Rll - CURSOR END REGISTER holds the scan line on which the cursor will end. If the same as RlO, then the cursor is only one line tall.

R12 - R13 : START ADDRESS REGISTERS HIGH and LOW contains the address of the first byte of RAM to be displayed after vertical retrace.

R14 - R15 : CURSOR REGISTERS HIGH and LOW contain the address of the cursor position in video memory.

R16 - R17 : LIGHT PEN REGISTERS HIGH and LOW hold the address appearing on the CRTC address lines when the light pen strobe input pulses high. The light pen has not been implemented on the Rabble 65.

NOTE: The character clock rate will be the product of the horizontal oscillator frequency and the total horizontal

. .

character times described in calculating the value for R0. The dot clock will be the product of the character rate clock and the width of the character block in columns. This may dictate a different dot clock for other screen formats.

#### DEBUGGING

If any malfunction is suspected in the operation of the video display controller, you should confirm that the following sections are operating correctly, for a malfunction in any of these areas can inhibit the normal operation of the CRTC. the areas to check are:-

CPU RAM 1 Monitor ROM. Refer to these sections if you are unsure of their operation.

Address lines from the CPU buss must reach both the video RAM and the CRTC. This is controlled by IC's 54, 55 and 57, 74LS157 data selectors. Check that the select input of each of these chips, pin 1, goes low when CS\$D000 is accessed, decimal 53248. When the select pin is low the address lines from the video RAM are connected to the CPU buss, and when this select line goes high the video RAM address lines are connected to the CRTC, 6845 IC57.

Data line transceiver IC73, 74LS245 is also controlled by the CS\$D000 line to connect the data buss to the CPU. Pin 19 of IC73, when low, enables the transceivers to permit data to flow in one direction or the other depending on the status of the R/w line. This enables data transfer between the video RAM and the CPU buss.

Ensure that the CS\$CO1C, decimal 49180, is reaching pin 25 of the CRTC, 6845 IC57. Test pin 24 for system address line A0, test pin 23 for phase 2 clock and pin 22 for the R/w signal. If all these signals are normal, and the reset line, pin 2 goes high for the duration the reset key is pressed, read the registers in the CRTC to ensure the expected values are contained therein. If the expected data is not in the registers, it is most likely that your screen is not displaying a readable format. in this case check that the following signals are present at the indicated test point.

Test point

Expected signal

. . .

| 1  | pin 3   | IC 82   | 74LS74  | 16MHz clock       |

|----|---------|---------|---------|-------------------|

| 2  | pin 7   | IC 69   | 74LS166 | 16MHz clock       |

| 3  | pin 13  | IC 69   | 74LS166 | 16MHz serial data |

| 4  | pin 15  | IC 69   | 74LS166 | character clock   |

| 5  | pin ll  | IC 71   | 74LS374 | character clock   |

| 6  | pin 7   | IC 86   | 74LS175 | cursor            |

| 7  | pin 15  | IC 86   | 74LS175 | display enable    |

| 8  | pin 1   | IC 81   | 7416    | H.Sync.           |

| 9  | pin 3   | IC 81   | 7416    | V.Sync.           |

| 10 | Video c | onnecto | r       | Composite Video.  |

In any of the above test points, should a signal be missing, check the previous stage, then work back through the circuitry to determine the faulty chip. Replace any suspect or faulty chips as required.

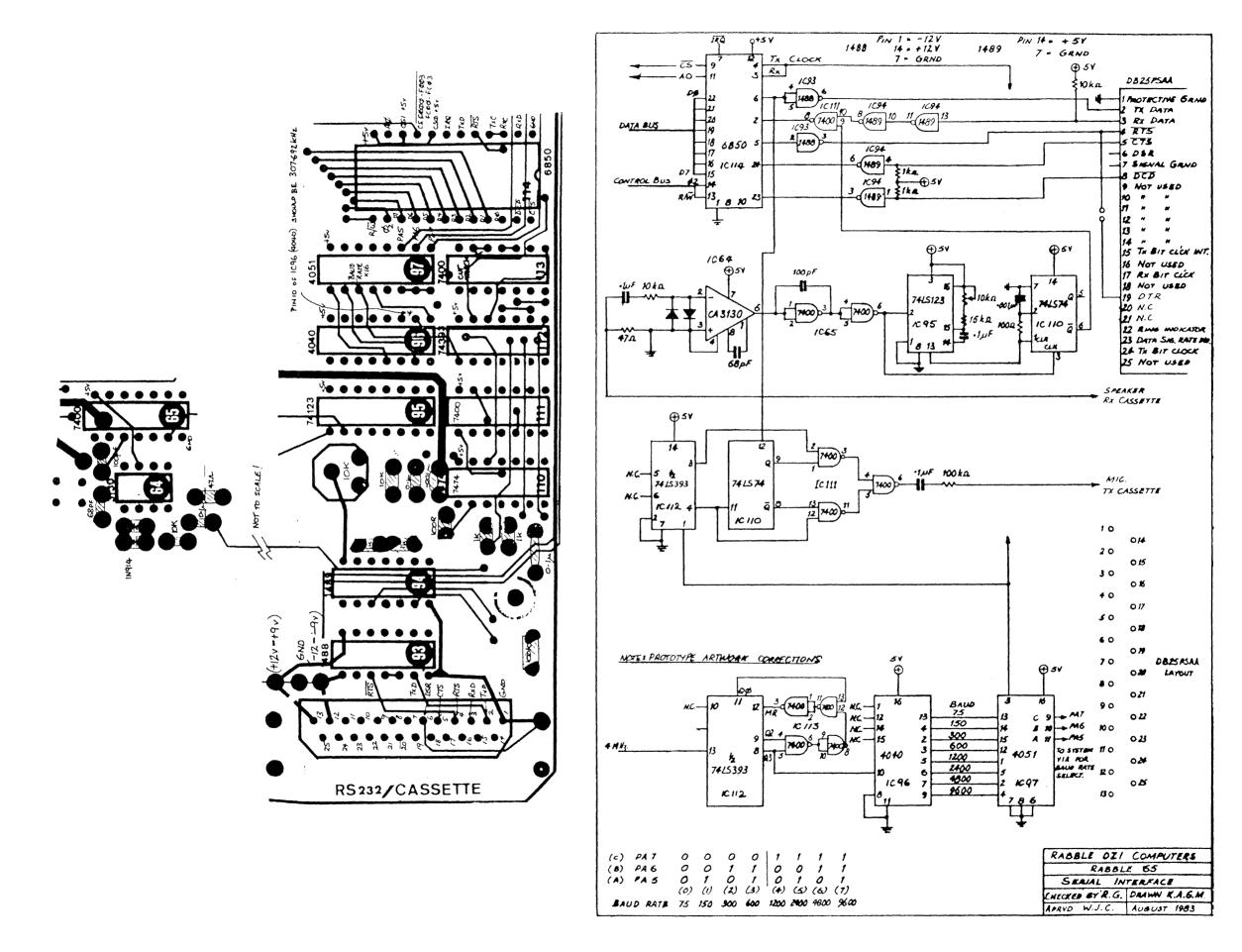

22.... CHAPTER 7

SERIAL INTERFACE

ASSEMBLY

The serial interface can be constructed as an RS232 interface, cassette interface or both. IC's 96, 97, 112, 113, and 114 are common to both modes. IC's 93 and 94 are used only in the RS232 mode and IC's 64, 65, 95, 110 and 111 are used only in the cassette mode.

To assemble this stage, all IC sockets should be mounted, then all discrete components required for the options selected. There are two resistors for the RS232 mode and five resistors, six capacitors, two diodes and a trimpot for the cassette mode. Once all relevant sockets and components are mounted, check all soldering for cleanliness before proceeding.

Insert IC's 90, 97, 112, 113 and 114. These chips are common to both modes. Test IC's 90, 97, 112 and 113 by checking that a waveform appears at pins 3 and 4 of the ACIA, IC 114. Test CS F000 / FC00 line on pin 9 of the ACIA by accessing \$F000 or \$FC00, decimal 61440 or 64512, to ensure that the chip will be selected.

Fit the relevant IC's for the RS232 and / or cassette interface as required. The RS232 requires no further adjustments. The cassette interface requires no adjustment for transmit and only one minor adjustment for receive. The adjustment detailed is to provide a receive signal conversion for 300 Baud data.

1. Connect 1200Hz from pin 3 of IC 112, 74LS393, to pin 20 of the Molex interface connector.

2. Connect a CRO to pin 13 of IC 95, 74LS123.

3. Adjust trimpot adjacent to IC 95 to obtain a 600uS positive going pulse on the CRO.

An alternative method of setting this input to an approximate setting if a CRO is not available, is as follows.

1. Connect a cassette recorder to the input of the serial port.

2. Load the prerecorded cassette programme, by pressing RESET then select ROM BASIC by pressing the space bar and then R. Type LOAD then press the return key.

3. Start the cassette recorder, and adjust the trimpot slowly

until the text appearing on the screen becomes readable. Rotate the trimpot until it starts to garble the data and then find the central point between the two extremes of "good" data. this completes the adjustment.

#### CIRCUIT DESCRIPTION

The RS232 / cassette interface is located at both \$F000 - F001 and \$FC00 - FC01. The RS232 I/O is via a 25 way standard connector, the DB25PSAA. The relevant connections are wired to the international standard.

The RS232 I/O has a software selectable Baud rate derived from the system 16MHz clock. This clock is divided down to 4MHz in the video block and fed to the Baud rate divider. The 74LS393, IC 112, and IC 113, 74LS00, divides the 4MHz clock by 13 to provide a 125nS pulse to the 4040, IC 96, every 3.25uS. The 4040 divides this by factors of 2 through to 256 to provide eight Baud rates from 75 to 9600 Baud.

Between the 4040, IC 96, and the ACIA, IC 114, is a demultiplexer, IC 97 a 4051. This device connects only one of the eight Baud rate outputs of the 4040 to the clock inputs of the ACIA. The selection is performed by setting up the system VIA port A bits 5 - 7 with the required data.

| Baud rate                                               | VIA PA Bit 7 6 5                                            |

|---------------------------------------------------------|-------------------------------------------------------------|

| 75<br>150<br>300<br>600<br>1200<br>2400<br>4800<br>9600 | 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0 |

| 5000                                                    | * * *                                                       |

The system VIA is located at \$C060 and is initialised on the standard system for 300 Baud. This also sets the cassette interface to 300 Baud.

The ACIA, IC 114 receives data from the data buss and converts this to the serial form and transmits it via the Tx data output to an RS232 line driver, MC1488 - IC 93. This line driver converts the TTL signal to true RS232 standard, which has a voltage swing of +12 volts to -9 volts, compared with a TTL voltage swing of +3.5 volts to +0.6 volts approximately This occurs when the R/w line is low. When the R/w line is high, data is read from the RS232 connector via the MC1489, IC 94, RS232 to TTL convertor, and the fed to the ACIA Rx input. The data on this input is clocked into the receive data register and when it is full a signal is generated within the the ACIA to indicate this status to the CPU. The ACIA loads this, now parallel, data onto the data buss at the request of the CPU, ie a read from the ACIA.

. . .

Three control signals are used with the ACIA for the RS232, the Data Carrier Detect (DCD), Clear To Send (CTS) are input signals and the Request To Send (RTS) is on output.

The DCD input is active low and it inhibits and initialises the receiver section of the ACIA when high. A low to high transition of the DCD initiates an interupt to the CPU to indicate the occurence of a loss of carrier when the Receiver Interupt Enable (RIE) is set.

The CTS input provides automatic control to the transmitting end of a communications link via the CTS, active low, by inhibiting the Transmitter Data Register Empty (TDRE) status bit.

The RTS output enables the CPU to control a peripheral, via the data buss. The RTS is active low and is controlled by the contents of the ACIA control register.

Other signals as shown on the circuit of the RS232 connector are not used on this system.

The cassette interface is designed to operate at 300 Baud and is initialised on system RESET to operate at this speed. 4800Hz is fed into IC 112, 74LS393, and this is divided down to provide 2400Hz and 1200Hz signals. The 2400Hz clock and the Tx data from the ACIA, IC 114 are fed to a 74LS74,D type flip flop and data inputs respectively. Each 833uS the information on the data input is clocked out of the flip flop and the Q output is set if the data is logic one and if the data is logic zero, the Q output is reset to logic o. If the Q output is set, the 2400Hz AND gate is enabled and thus eight cycles of the 2400Hz signal are output to the cassette via pin 3 of the Molex connector. If a logic zero is input to the flip flop the Q output is reset and the 1200Hz gate is enabled, causing four cycles of 1200Hz to be output to the cassette.

To read data from cassette the information is fed via pin 5 of the Molex connector. This signal is clipped to 0.6 volts P-P by the IN914 diodes prior to amplification by the CA3130, IC 64, amplifier. The signal is then buffered by a pair of 74LS00 gates, IC 65, prior to being fed to the retriggerable monostable multivibrator IC 95, 74LS123, and the clock input of flip flop IC 110, 74LS74. These clock signals are 2400Hz, to represent a logic one data bit or 1200Hz for a logic zero data bit. With each positive going pulse into the 74LS123, IC 95, a fixed length pulse is fed to the clear data input of the flip flop, IC 110, as well as its data input. This data is transferred to the Q output of the flip flop on the next clock pulse input to the clock input of the flip flop. For a 2400Hz signal the 74LS123 monostable is retriggered prior to it completing its output pulse. The duration of the monostable pulse is approximately 600us. For 2400Hz signal input the 74LS123 is reset each 417uS, thus causing the output to remain at logic one. A 1200Hz signal, which represents logic zero, has a period of 833uS. Thus for a 1200Hz input signal, the Ql output of IC 95, 74LS123, goes high for 600uS and the Q output of IC 110, 74LS74, has the previous signal data transferred to it. At the next positive going edge of the 1200Hz signal the monostable is reset and the logic zero signal at the data input, pin 12 of IC 110, is transferred to the Q output and carried to the ACIA, IC 114, serial input, pin 2.

. . . .

24....

#### DEBUGGING

The programmable divider is a chain of dividers followed by a one-of-eight selector. IC 112, 74LS393, should have a 4MHz square wave input to pin 13, and a pulse output of approximately 125nS width each 3.25uS. This pulse should be present on pin 10 of IC 96, 4040. The outputs of the 4040 should exhibit a frequency of 16 times the Baud rate shown on that output. The demultiplexer, IC 97 4051, will have an output frequency of 16 times the actual selected Baud rate. The selected Baud rate is determined by IC 107, VIA, and the table of values is shown in the circuit description of this chapter. This area must function correctly before the rest of the serial interface can be expected to perform.

The ACIA, IC 114, has eight data lines which should have data signals to it when written to. Control signals should be present, these are phase 2 clock, pin 2; R/w, pin 13; address line A0, pin 11; and CS on pin 9. The CS line can be accessed by addresses \$F000 or \$FC00, decimal 61440 or 64512.

Write to the ACIA after a standard system initialisation and ensure that data is output in serial format on pin 6 of IC 114, ACIA. This data should also be found on pin 2 of the DB25PSAA connector.

Connect pins 2 and 3 of the DB25PSAA connector together and then write to the ACIA again and the serial data should appear on pin 2 of the ACIA, IC 114.

Pins 5 and 8 of the DB25PSAA connector should be floating high and the inputs of the ACIA, pins 24 and 23 of IC 114, should be low. These are the inverting, level translator gates of IC 94, MC1489.

After ensuring that the RS232 section works, ensure that the 1200Hz and 2400Hz signals are present on IC 112, 74LS393, pins 4 and 3 respectively. Serial data at 300 Baud should be present on pin 12 of IC 110, 74LS74 and the outputs on pins 9 and 10 should toggle with data changes. Pin 9 of IC 110 should be logic one when a data bit is logic one and pin 10 should be logic zero when a data bit is logic zero. Follow this data stream through the 74LS00 gates, IC 111, and finally to appear on pin 5 of the Molex connector.

To test the cassette receiver connect pins 3 and 5 of the Molex connector together and output data to the port. Check that the signal reaches pin 2 of the CA3130, IC 64, and that it does not exceed 0.7 volts P-P. The input waveform from cassette recorders may be somewhat distorted, but should square up once they pass through this amplifier. Pin 6 of IC 64 should exhibit a square waveform alternating between 1200Hz and 2400Hz. This same signal should appear on pin 2 of IC 95, 74LS123 monostable multivibrator, and also on pin 3 of IC 110, 74LS74 flip flop.

If all is well at this point, ensure that the set up instructions detailed in the assembly instructions have been carried out, or if unsure, carry out the set up again.

. . . .

26.... Data into pin 13 of IC 110, 74LS74, should be data in serial format at the rate of 300 Baud. This data stream is also expected at pin 6 of IC 110, prior to ORing with the RS232 signal, from the gates of IC 94. This signal is then fed to the ACIA at pin 2.

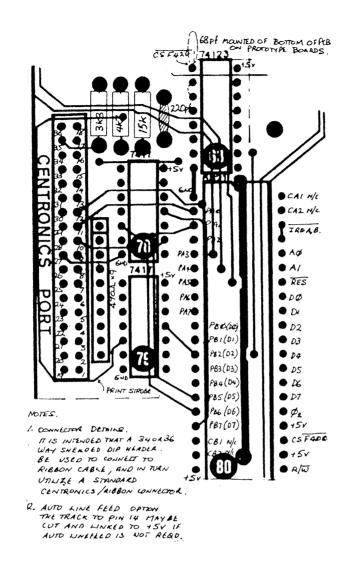

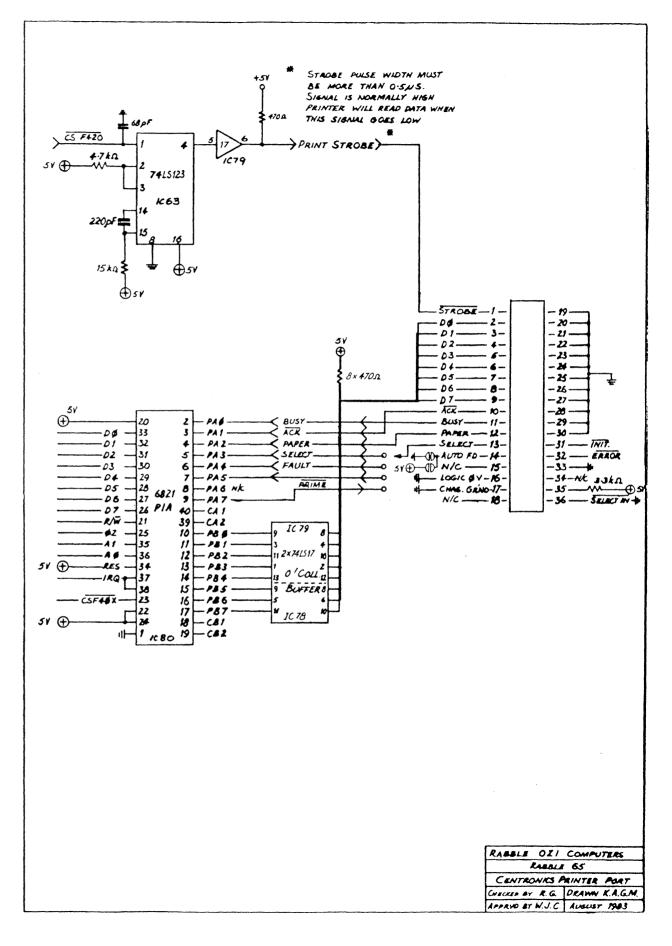

#### 27.... CHAPTER 8

CENTRONICS PARALLEL PORT

#### ASSEMBLY

This section of the Rabble 65 computer is straight-forward, as there are no timing adjustments to be performed. The interface consists of only four chips, a connector, three resistors one resistor pack and a capacitor. To assemble this section, ensure that the Centronics port connector and the IC sockets, No's 63, 78, 79 and 80, are installed. Fit into position the discrete components and the resistor package, taking care to orientate the resistor package the correct way around. Pin 1 of the resistor package will be identified by an indentation on the package at the pin one end or with a spot at the same end, this end is fitted to the rear of the board, away from the keyboard. Check all solder connections to ensure no tracks are shorted or pins are left unsoldered. If neccessary clean excess resin from the board with a cloth dampened with methylated spirits. When satisfied all is well insert IC's 63 -74LS123, 78 and 79 - 7417, and 80 - 6821.

#### CIRCUIT DESCRIPTION

The heart of the Centronics interface is the 6821, IC 80, which is a PIA. This chip is located at memory address locations F400 - F403, decimal 62464 - 62467, and contains registers which are initialised by the system after resetting. Address lines A0 and A1 are used to select the appropriate register when the CSF40x line is held low. The R/w line is used to store data from the data buss into the registers during a write cycle or to read data during a read cycle. The reading or writing to the output registers of the PIA causes the transfer of data to or from the Centronics port. Port A output register is located at \$F400 and port B at \$F402.

The PIA in this application is organised to set up Port A bits 0 - 5 as inputs, and bit 7 as an output. Port B is organised to set all bits as outputs. Port A bit 6 is unused.

CA1, CA2, CB1 and CB2 are not extended to the Centronics port, and thus an interupt request  $(IR\Omega)$  cannot be generated.

The PIA is automatically reset on system power up, and is initialised by the system monitor.

All data and control signals output by the Centronics interface are buffered IC's 78 and 79, 7417 - open collector buffers, with pull up resistors on their outputs. This provides around 20mA of sinking capability, which will suit a wide range of parallel printers.

The 74LS123, IC 63, retriggerable monostable multivibrator is used to provide a STROBE signal to advise the printer that valid data is on the Centronics data buss, at that point of time. The STROBE signal is initiated by a CPU access to address \$F420, decimal 62496. This causes the input line CSF42x to IC 63 to go low and enables the monostable to generate a pulse of around luS, determined by the values of the R and C of the monostable. In our application the resistor is 15Kohms and the capacitor is 220pF. The STROBE signal is a negative going pulse from the output of IC 63, and is bufferred by the 7417 buffer prior to being output on the Centronics connector.

To output data to the printer the system software reads the data on Port A and tests that the printer is ready to receive a character or byte of information, and, if ready, a data byte is loaded into Port B output register of the PIA, IC 80. This then appears on the Centronics interface connector. A print STROBE pulse is then generated as described earlier, advising the printer to read the data from the data buss. The printer then generates a printer BUSY signal to prevent the Rabble 65 from outputting any more characters. This condition is held until the printer has completed printing the character or has stored it in its own memory buffer. During the BUSY signal to be cleared before setting the PIA up for the next character to be printed.

Other signals are available on the Centronics printer to indicate the status of the printer, and can be tested the system software as required. These are FAULT, SELECT, PAPER OUT and ACKNOWLEDGE.

#### DEBUGGING

Ensure that the STROBE signal is present by writing to \$F420 and monitoring pin 1 of the Centronics connector with a CRO or logic probe. A negative going pulse of greater than 0.5uS should be visible each time \$F420 is accessed. If this is missing check for it at the output of IC 63, pin 4, and if still missing check that the CSF420 signal is reaching pin 1 of IC 63, to enable the monostable. Replace IC 63, 79 or associated components as required, to restore the STROBE pulse.

Assuming the STROBE pulse is normal, check that there are no irregularities in the printers operation, ensure that it is turned on and selected for the correct format etc. If it has a self test function then ensure it passes that test. Next check with a CRO or logic probe that the BUSY line is low, if not the CPU will wait for the printer to send it high before attempting to output a character.

If all PIA input signals test correctly, initialise the PIA by resetting the CPU with the standard Rabble 65 monitor, the RA65. Examine the relevant memory locations to ensure that the PIA is functioning correctly.

| Address | Data |                           |

|---------|------|---------------------------|

| F400    | 0 0  | with printer disconnected |

| F401    | 04   |                           |

| F402    | XX   | depends on data being     |

#### 28....

29.... output

#### F403

04

Note the high bit of F401 and F403 may or may not be set.

Now write \$FF to location \$F402, then read it back again to ensure that the Port is latching the data. It should read \$FF. If the data in the PIA is not correct, it may indicate a faulty PIA, which should be replaced, or that one or more of the control signals is not reaching the PIA, in which case the source of the control signal should be tested.

With your logic probe or CRO check that the reset line, pin 34 of IC 80, is high and that the data lines are all pulsing, ie the CPU data buss lines. If any of these are doubtful, check the equivalent line in the RAM section. This will indicate whether or not there is an open circuit track on the board. Ensure that the R/w line, the phase 2 clock, A0 and Al are also present. Any missing or static signals should be traced back towards the CPU and repaired.

Finally check that the PIA is selected with a logic low pulse on pin 23 of the PIA, by performing a read or write to to the PIA at address \$F40x.

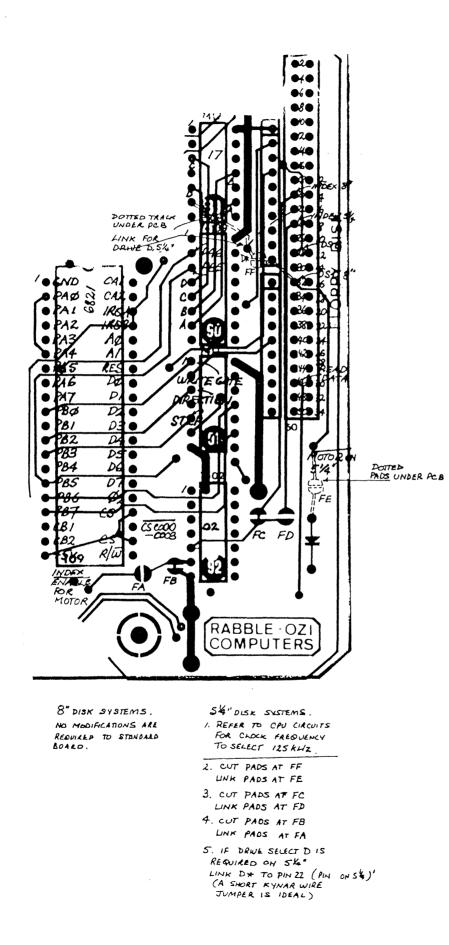

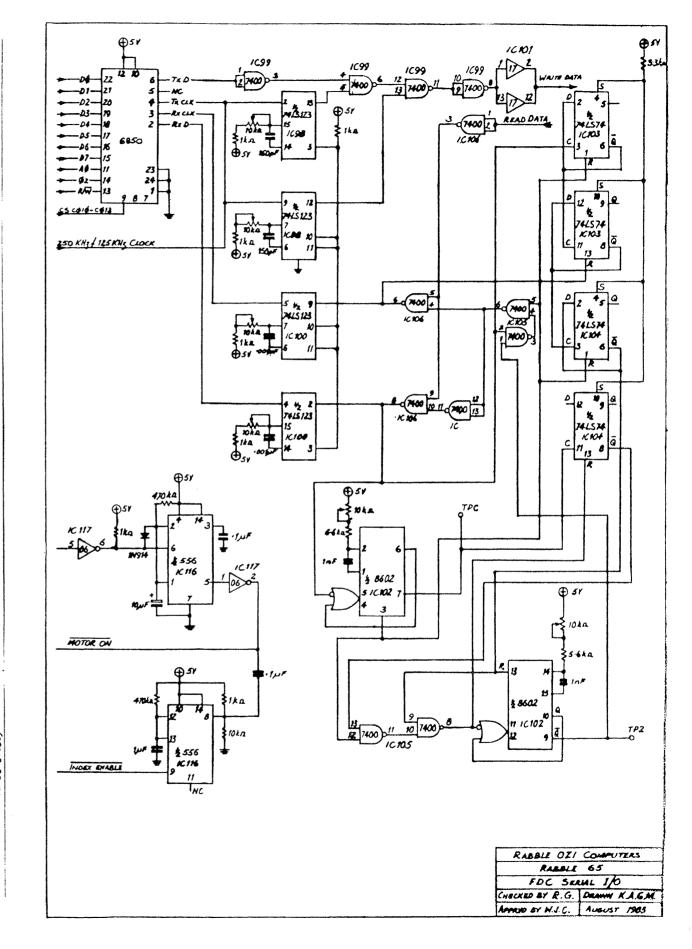

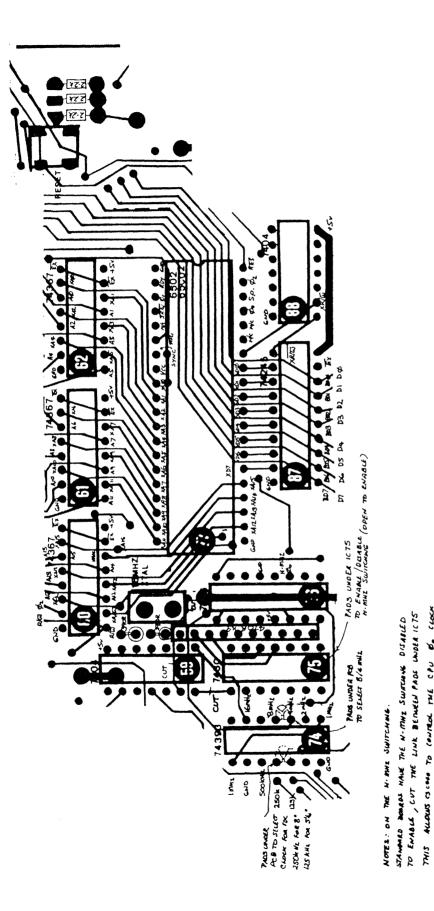

30.... CHAPTER 9

FLOPPY DISC CONTROLLER PARALLEL SECTION

ASSEMBLY

Fit IC sockets for IC's 89 - 92 and 109. Install the two resistor packs adjacent to the FDC connector, taking care to orientate the resistor pack correctly, pin 1 is marked with an indentation or spot at that end. The FDC connector should also be installed at this time. After all components are soldered into position, check all joints for solder bridges, missed pins etc., if neccessary clean away excess resin deposits.

The board is configured in manufacture to suit 8" mini floppies. If it is desired to use 5.25" mini floppies a number of track cuts and links need to be performed. The connections to the 50 way DIP connector for the FDC which require changing are as follows:-

INDEX pin 20 of the FDC connector is transferred to pin 24 of the connector.

DRIVE SELECT D is transferred from pin 32 to pin 22 for 5.25" operation. pin 22 is normally reserved for the READY line which is used on some drives and is not required for the Rabble 65.

MOTOR ON Pin 32 is connected to the motor control signal to provide control over d-c drive motors on 5.25" drives.

INDEX ENABLE is cut and linked as shown on the circuit to allow the d-c motor to accelerate up to normal operating speed before allowing the FDC to perform any data transfers to or from the disk. This change should always be carried out with the MOTOR ON change.

Each of these options is shown on the circuit and overlay diagrams opposite.

The connecting cable to either disk drive size should be via a 50 way cable. The connector on the 8" drives is a 50 way connector and the connections are pin for pin equivalent. The 5.25" drives have a 34 way connector to interface with the Rabble 65. To interface this drive, connect a 50 way cable as described for the 8" version, then prepare to connect the 34 way connector to the other end. The cable should be split between wire 16 and 17 at the drive end and pared back to allow for the number of drives being connected. The 16 wire side of the cable can be cut off, and the 34 wire side of the cable can be terminated on the 34 way socket for the 5.25" drive. All odd numbered connections of both ends of the cables of both sized drives are ground connections for the FDC and drive. Test that the cable and sockets are correctly orientated before 31.... connecting.

Once all connections and cables are completed, IC's 89 - 92 and IC 109 should be inserted into their respective sockets to complete the assembly of the parallel section of the FDC.

To change operation from 8" drives to 5.25" drives, a number of tracks need to be cut and links installed. The points where these alterations are made are highlighted on the printed circuit board by a circular pad, cut through the centre. Some of these pads have a link fitted during manufacture, others are open across the two halves. To cut a link use a sharp hobby knife and make two parallel cuts through the centre of the pad cutting across the link, and then lift the small section of track away from the board. To fit a link, carefully scrape away the solder resist on the two halves of the desired pad and then solder a short piece of wire across the gap.

The tracks affected by the different drive requirements are connected to :-

| FDC PIN NO. | 8 "      | 5 <b>.25"</b> | No.Cuts | / | Links. |

|-------------|----------|---------------|---------|---|--------|

| 20          | INDEX    | IN-USE        |         | 1 |        |

| 22          | READY    | D.S.D         | 0       | 1 | 1      |

| 24          | Not used | INDEX         | 0       | / | 1      |

| 32          | D.S.D    | MOTOR ON      | 1       | / | 1      |

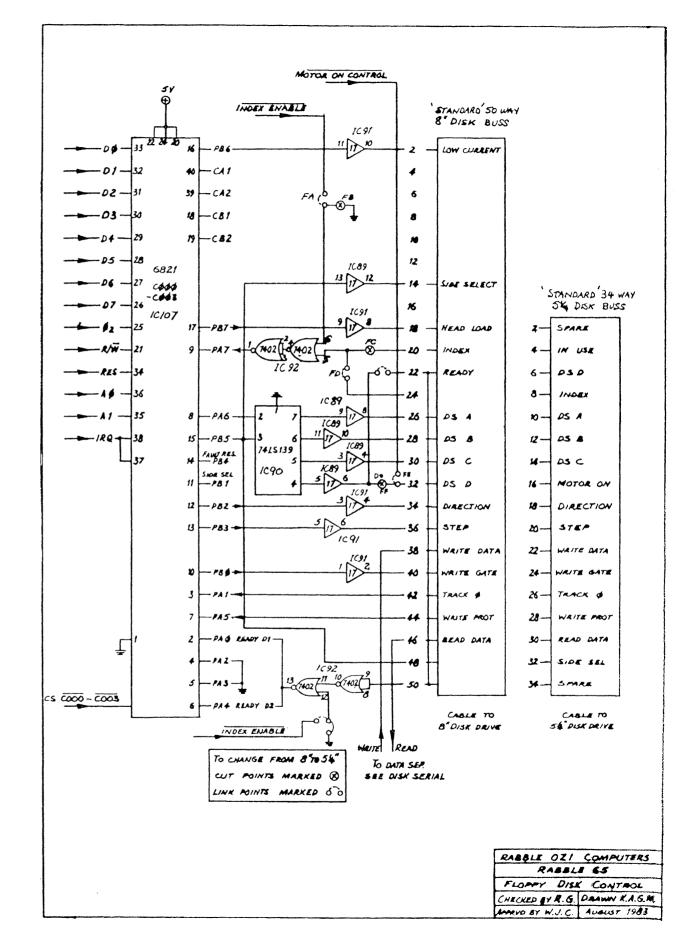

CIRCUIT DESCRIPTION

The FDC contains four main sections. Briefly their functions are:-

1. PIA A 6821 peripheral interface adaptor. This device isused to control the mechanical movements of the disk drives and to inform the CPU of the status of the disk drives.

2. ACIA A 6850 asynchronous communications interface adaptor, is used to transmit and receive data to and from the disk drive as required by the computer. The ACIA also converts this data from eight bit parallel to serial format when writing to the disk, and from serial to parallel when reading from the disk.

3. DATA SEPARATOR The function of this section is to separate the data from the stream of pulses coming from the disk. A clock pulse is interleaved with each data bit which is stored on the disk.

4. MOTOR CONTROL This function is provided to save wear on the d-c drive motors of 5.25" disk drives. It is a timer network which activates the drive motors for about 3 seconds each time the FDC PIA is accessed. A delay is also inserted in the INDEX ENABLE line to provide motor speed to reach normal before data is read from the disk.

• (

The data lines for both the ACIA and the PIA are in parallel. Their address locations are \$C010 - C011 and \$C000 - C003 respectively, decimal values for these locations are 49168 - 49169 and 49152 - 49155.

PBO ( Port B line 0 ), is the write gate. This gate, like all other signals in the FDC, is active low, ie the write gate becomes active or operational when the logic level of this gate is zero. The write gate when active switches the electronics in the disk drive ready to write data to the drive's head, hence the disk. However, the software for the FDC tests that the disk in the drive is not write protected. If it is write protected then the write gate is not changed and the electronics in the drive will remain in the read mode.

PB2, PB3. These are the direction and step lines that are used to position the head of the drive over the desired track of the disk. The stepping motor in the drive moves the head one position each time the step line is sent a low going pulse. The direction that the step motor drives the head is determined by the logic level on the direction line.

PB5, PA6 The PIA is organised to select one of four drives. This is controlled by PB5 and PA6 outputs, which are input to a 74LS139 to decode these two lines to provide four discrete drive lines. These lines each bufferred by a gate of a 7417, open collector buffer, and connected to the drives of the FDC connector cable.

PB6 This is the low current line which is used to reduce the write current to the head on the inner tracks of some 76 and 80 track drives. The electronics controlling the write current is contained in the disk drive itself and the low current brings it into operation if required.

PB7 HEAD LOAD, places the head assembly onto the disk media. When a drive has its drive motor running continuously, the raising of the head when not required to transfer data, significantly reduces the amount of wear on both the head and the disk.

All of port B and also PA6 of the PIA are configured as outputs to send control signals to the disk drive. Port A, with the exception of PA6, reads control information from the disk drive.

PAO, PA2, PA3 and PA4 are unused and their lines are tied low.

PAL TRACK 00 is used to indicate when the head of the disk drive is positioned over the outermost track of the disk, which is track 00.

PA5 WRITE PROTECT goes low when the disk in the drive has been write protected. On 5.25" disks this is done by fitting an opaque label over the write protect indent on the side of the

33....

disk cover. On 8" disks the write protect is performed by removing the opaque label on the front edge of the disk cover. When this line is low the FDC is prevented from attempting to write to the disk.

PA7 INDEX / SECTOR is used on soft sectored disks to inform the FDC the precise angular position of the disk in relationship to that during the original write operation to the disk. The index pulse is generated once each revolution of the disk by an opto coupled device, looking through a hole in the cover of the disk and the disk itself as the hole rotates around to line up with these other holes.

## PARALLEL SECTION FDC DEBUGGING

The parallel section of the FDC is a relatively simple stage of the Rabble 65, containing only five chips and a couple of resistor packages.

If it is suspected that a fault exists with this section of the FDC, test which of the functions are operable in the disk drive, controlled by the PIA, IC 109. If some functions operate then it is unlikely that the problem is within the PIA. Check all of the open collector buffers of the 7417's, IC's 89 and 91, to ensure that signals produced by the PIA are being output to the FDC connector.

If drives are not being selected correctly, then it is possible that IC 90, the 74LS139, could be at fault or that the drives may be internally configured to be a drive device number other than expected. Check that the selected drive output is being decoded correctly from the two inputs on pins 2 and 3 of the 74LS139. Outputs on this chip are on pins 4, 5, 6 and 7, which are then fed via the open collector buffers, IC's 89 and 91, to the FDC connector.

If nothing appears to operate correctly, check that all control signals are reaching IC 109, PIA. These are the CSC000, decimal 49152, for four consecutive locations on pin 23. Address lines A0 and A1 on pins 36 and 35 of the PIA. Check that all data lines are positively connected to the data buss, and that the R/w, and phase 2 clock signals are present.

If all appears well, initialise the PIA and alter the contents of the data registers, check that the data written into the output registers of the PIA are stored correctly. If this tests out correctly, then any fault must lie external to this section of the FDC. Refer to the serial section of the FDC for more information.

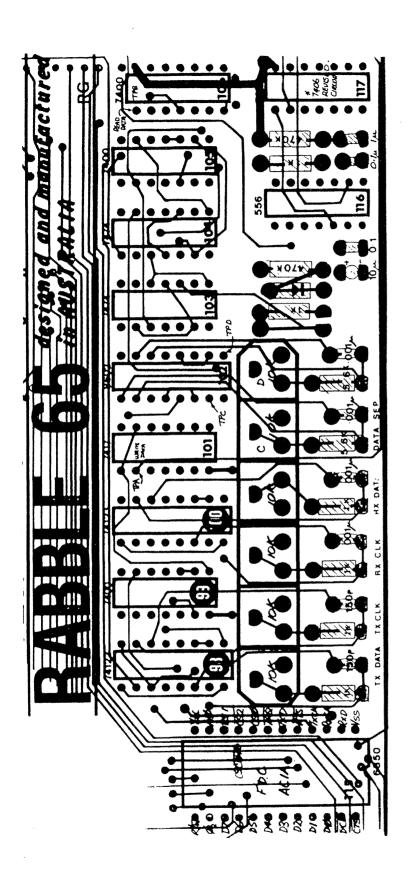

34.... FLOPPY DISK CONTROLLER SERIAL SECTION

ASSEMBLY

Fit sockets for IC's 98 - 106 and 115 - 117, also fit the discrete components as shown on the component overlay. Take care with the orientation of the diode. After soldering in all components, once again check your work thoroughly and clean the board if neccessary.

The serial port is set up for 76 - 80 track drives during manufacture, but can be reconfigured for 40 track drives if neccessary.

All 8" drives are 76 or 80 track drives, standard 5.25" drives are 37 or 40 track drives. Some 5.25" drives are of a 96 track per inch density, and are a 76 or 80 track drive.

Should it be required to operate standard 5.25" drives, it will be neccessary to change the clock speed for the ACIA on the FDC serial port. This is done by cutting the track on the bottom of the board at pin 4 of IC 74, refer to the CPU section circuit diagram for this part of the Circuit, and connect the isolated track to pin 3 of IC 74. This will provide a serial clock rate of 125KHz in lieu of 250KHz.

Note that conversion of the serial section of the FDC to standard 5.25" operation requires that simultaneous changes be made to the parallel section of the FDC.

Insert the nominated chips for this section and proceed to the serial circuit description to set up the six trimpots. It is essential to have access to a cathode ray oscilloscope with a bandwidth of at least 15MHz, to be able to set up the narrow pulse widths accurately.

CIRCUIT DESCRIPTION

The ACIA is, as stated earlier, used to convert parallel data to serial data and vice versa. The serial data is given a few extra bits of information, to provide a very high reliability factor. The ACIA is configured to provide eleven bits of information for each eight bit byte of data. The format of this data is:-

one start bit

eight data bits

one even parity bit

one stop bit

The serial clock rate is 250KHz for 76 - 80 track drives, in 8" and 5.25" formats. The standard 5.25" drive operates with a clock rate of 125KHz. Each 4uS a 250nS pulse is sent to the drive to be recorded on the disk. This is called the clock pulse, and is used as a means of keeping the data separator, on replay, informed of the exact timing of the disk,

to maintain a high degree of accuracy. During recording, data pulses are sent to the disk only when the data bit is at logic one, otherwise no data pulse is recorded on the disk. The data pulse is identical to the clock pulse and is sent 2uS after the start of the clock pulse ( if the data pulse is a logic one ). Note that for the standard 5.25" drives, the times are doubled and the overall clock rate is halved.

The clock and data pulses are generated by a retriggerable one shot monostable, which is controlled by the 250KHz clock (125KHz for standard 5.25"). The pulse widths are adjustable to provide the ability to change between the two drive formats.

On reading information from the drive, the data stream contains a mixture of clock and data pulses, this is called raw data. A data separator is included on the Rabble 65 to recover the data only stream and feeds this to the the FDC ACIA. The separated clock signals are used to clock the data stream into the ACIA. Both these signals travel via pulse modifying networks contained in IC 100, a 74LS123.

The raw data from the drive is inverted and fed to the control gates of the separate clock and separate data outputs from the data separater. The output of the separate clock gate sets the 8602, IC 102, one shot by pulling pin 11 low, this sets the 2.9uS one shot. The 8602 output, pin 9 IC 102, goes low causing IC 105, 74LS00, pin 3 to go high and pin 6 goes low and inhibits the separate clock gate for 2.9uS, which is long enough to allow the next pulse, which is a data pulse if it is present, not to be seen at the separate clock output. However, the separate data gate input is ready to permit this pulse to be passed through as a separated data bit. At the end of the 2.9uS time period pin 6 of the 74LS00, IC 105, goes high again to enable the separate clock gate, whilst inhibiting the separate data gate. Since the interval between clock pulses is 4uS, the circuit is reset when the next pulse is seen.